Vailable online at www.sciencedirect.com

# SciVerse ScienceDirect

Energy Procedia 27 (2012) 604 - 609

SiliconPV: April 03-05, 2012, Leuven, Belgium

# Introducing XIS, a new integrated device and module concept

J.A.M. van Roosmalen\*, P.C.P. Bronsveld, A.W. Weeber

ECN Solar Energy, P.O. Box 1, NL-1755 ZG Petten, The Netherlands

#### Abstract

In this paper we introduce a new device concept for high efficiency, low cost, wafer-based silicon solar cells. To significantly lower the costs of Si photovoltaics, high efficiencies and large reductions in the bill of materials, especially for metals and silicon, are required. The reduction of the amount of metal in wafer-based silicon modules requires adaptation of the device architecture into low-current devices. Basically, this comes down to reducing cell dimensions in the direction of current flow. The XIS (Crystalline Silicon Interconnected Strips) device concept addresses this significant reduction in the consumption of metals and enables the use of ultra-thin silicon wafers. In combination with a high efficiency back-contact heterojunction device geometry a cost reduction to below  $0.5~\mathrm{C/Wp}$  is foreseen. The integrated device and module concept can be realized with standard industrial production processes. The concept relies on the high efficiencies that can be achieved with crystalline silicon wafers, in combination with the high throughput that can be achieved with thin-film manufacturing technology. First devices have been realized demonstrating the principle of a series connected back contact hybrid silicon heterojunction module concept.

© 2012 Published by Elsevier Ltd. Selection and peer-review under responsibility of the scientific committee of the SiliconPV 2012 conference.

Keywords: Heterojunction; back contact; module concept; thin wafers

#### 1. Introduction

In recent years, PV system prices have gone down rapidly, reaching grid parity levels. Meanwhile industry faces competitive times and focus is on market share. However, we still have a large task to increase efficiency in combination with lower costs to realize a true sustainable solution for large scale electricity generation. Materials supply chain security, price stability and possible scarcity will be important as well. Even with the use of earth abundant materials, the scale that is necessary to install terawatts of PV and the economics related to that force the minimization of materials consumption. To reach high efficiencies crystalline silicon wafer technology is one of the most important candidates because of the high material quality that can be reached in the purification process, which is already available at large scale production. The XIS concept (XIS stands for Crystalline Silicon (X)

\* Corresponding author: Tel: +31885154782; fax: +31885158214 *E-mail address*: vanroosmalen@ecn.nl

Interconnected Strips) combines the high efficiency of crystalline silicon wafer technology with a much reduced bill of materials and high throughput, such as large area processing as is possible with thin film PV technologies.

# 2. The XIS concept

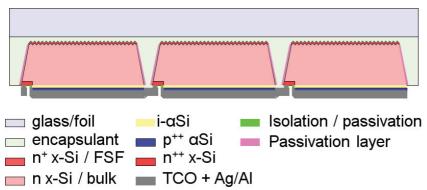

To be able to reduce the amount of metal that is used in PV cells and modules, the current needs to be reduced. This is done by reduction of the cell size, e.g. dividing 156 x 156 mm² wafers into 52 strips of 3 mm width and connecting them in series. In this way, low currents and high voltages are realized. It is proposed that the individual strips are not handled separately. Before strip formation, the wafers are adhered to a superstrate. First, the front sides of the wafers are processed, e.g. texture, FSF, and passivation. Then, the wafers are bonded to the sun-receiving superstrate. In this way, only a minimum amount of process steps needs to be performed on wafer level, enabling the use of ultra-thin wafers (20-50 µm) and therefore reducing the costs of silicon, still the largest fraction of the materials costs. Conceptually, there are interesting similarities with the i-module approach [1]. In the XIS approach, after bonding, processing is done on module level, enabling high throughput: separation of the strips, junction and BSF formation, metallization and interconnection (isolation). Given the relatively small cell sizes, the edges of the cell will need to be well-passivated. After bonding the processing temperature is restricted to the maximum temperature tolerated by the (transparent) adhesive, e.g. around 200 °C in the case of silicones. Therefore, back contact heterojunction (BC-HJ) solar cells are used, see Fig 1.

Fig 1. Schematic cross section of a XIS module (not on scale) showing a series connection of three out of many strips. Individual cells / strips typically have a width of one to a few mm only

The cells as displayed in Fig 1 have a heterojunction emitter consisting of intrinsic (i-aSi) and p-type (p<sup>++</sup> aSi) amorphous silicon extending over the largest part of the rear surface for efficient collection of minority carriers. The BSF is located at the edge of the rear surface. Majority carrier transport can be realized through bulk and front surface field (FSF). In this way a new concept for hybrid back contact silicon heterojunction solar cells are realized and introduced in this paper. The front surface is arranged for optimal light coupling, e.g. by a random pyramid texture and (passivating) anti-reflection coating (ARC, not shown) and is laminated to the transparent superstrate (sunny side) with a transparent encapsulant. To isolate the cells from each other grooves are made in the wafers. The sidewalls of the grooves are passivated. A metal and transparent conducting oxide (TCO, optional) provide a series connection over the groove to the adjacent cell. Isolation between emitter and BSF contacts is arranged over the BSF area. The module can be completed with a backsheet foil or glass plate (not shown).

The schematic cross section as is shown in Fig 1 and the integrated cell and module architecture that are described are examples of the possibilities to realize XIS devices. Other options include e.g. bonding to the rear substrate, full back contact heterojunction devices, i.e. making use of an amorphous silicon BSF as well as emitter, options for grooves and their passivation, contacting and isolation, among others.

# 3. High efficiencies for BC-HJ devices

Since the emitter formation of the solar cells is foreseen after bonding of the wafers to the glass superstrate, the options for emitter formation are more restricted than with standard solar cells. However, Si HJ solar cells have demonstrated to have an excellent efficiency potential. The highest efficiency reported to date is 23.7% [2] on an area of 100.7 cm2. The XIS concept differs in several aspects from standard HJ devices, like those of Sanyo [2].

- Back contact. In front junction heterojunction devices light absorption from the TCO and amorphous silicon layers slightly lower the efficiency. In addition, there is shading by the screen printed metal pattern. In back contact devices both are not present. The efficiency potential for BC-HJ structures was been modelled by Das et al. [3] to be 24-26%. Sanyo is aiming for  $\eta = 25\%$  laboratory devices [2]. Recently, Mingirulli et al. [4] have obtained an excellent  $\eta = 20.2\%$  for a BC-HJ device, demonstrating for the first time that BC-HJ devices can also reach high efficiencies in practice.

- Thin wafers. The aim of the XIS concept is to enable the use of thin wafers, e.g. with 20-50 μm thickness (with excellent light trapping), to reduce the Si material consumption. In itself, the concept is not restricted to thin wafers and high efficiencies can also be obtained with standard wafer thicknesses. Due to the excellent surface passivation, it can be expected that for heterojunction devices efficiencies do not decrease with decreasing wafer thickness. They might even slightly increase due to the higher voltage. In fact, the record efficiency obtained by Sanyo has been obtained with a 98 μm thick wafer, compared to the more than 200 μm thick wafer for the previous record of η = 23.0% [2].

- Hybrid technology. For production purposes, it might be interesting to combine a heterojunction emitter with a diffused BSF rather than a hetero-BSF as is used in standard (IBC) heterojunction solar cells, due to more degrees of freedom with respect to masking and aligning. Both options are possible for the XIS concept.

### 4. Materials cost reduction

The main purpose of XIS is to reduce the bill of materials. The bill of materials for PV modules can be assigned to three main functionalities: the photovoltaic effect, electrical transport, and packaging, including weather protection and isolation. The main advantages of XIS are the reduction of the amount of metal required for electrical transport on the cells, from cell to cell and to the junction box and enabling the use of thin wafers, lowering the amount of silicon required.

In standard cells, Ag and Al screen printing pastes are used for metallization on the cells and copper tabs and bussing for interconnection between the cells and to the junction box. Due to the high currents up to 9 A for the 156 x 156 mm2 large wafers, large amounts of metals are used in order to reduce series resistance and FF losses on cell and module level. By reducing the cell width to only a few mm and organizing the transport direction perpendicular to the cell width, less than a  $\mu$ m of metal is necessary to transport the power from cell to cell. It is assumed that series connection can be achieved with sputtered Al. In this way, a high voltage is built up, which also contributes to a reduction of the amount of metal that is necessary for the bussing to connect the wafers to the junction box. Furthermore, no expensive Ag is needed anymore! Combinations of series and parallel connections allow to regulate the module voltage.

The amount of silicon that is necessary for present-day modules is estimated at about 6 g/Wp, although a large part of which does not end up in the module. For the XIS potential calculation, it is assumed that the wafer thickness is 50  $\mu$ m (although perhaps even 20  $\mu$ m is possible in the future) and that there are no kerf losses or other losses. This is an idealized situation. The silicon price is chosen at 40 €/kg. Amounts and prices of metals are estimated from a reference H-pattern / metal wrap through cell and module technology. In Table 1 a comparison between the rough data of the reference module and XIS is made. This delivers a rough estimates for the bill of materials. Processing costs are not included. It can clearly be seen both from the silicon aspect and from the metal consumption, XIS is an interesting way forward.

| Table 1. Comparison between e | estimated materials conten | it and bill of materials f | for reference H-pattern/MWT | modules and XIS |

|-------------------------------|----------------------------|----------------------------|-----------------------------|-----------------|

| *                             |                            |                            | *                           |                 |

| Material   | Reference module | XIS              |         |                  |

|------------|------------------|------------------|---------|------------------|

|            | $g/m^2$          | €/m <sup>2</sup> | $g/m^2$ | €/m <sup>2</sup> |

| Si         | 1200             | 48.0             | 116     | 4.7              |

| Cu         | 330              | 9.9              | -       | -                |

| Ag         | 13               | 6.2              | -       | -                |

| Al         | 70               | 5.8              | 2.7     | 0.2              |

| Al-bussing | -                | =                | 30      | 2.2              |

#### 5. Producability, revolution or evolution?

Although the XIS concept appears to be quite different from standard silicon wafer technology, the development towards XIS can be regarded more as an evolution rather than a revolution. The main component that is added by XIS is the full module area processing. After processing the wafers up to the front side, the wafers are transferred to the glass superstrate and from there on processed on the module level. These processes are already available in the thin film PV industry and the display technology. Laser processes for accurate interconnection and isolation on full module level are well known in most thin film PV technologies, including a-Si, CdTe and CIGS and large area laser micromachining with little damage is demonstrated e.g. in lens fabrication [5]. In thin film PV and display technology large area deposition of semiconductors with high accuracy has been developed already. In plasma display technology, screen printing on large areas, 2x2 m2, with accuracies approaching 10 µm is industry practice [6].

# 6. First XIS demonstration devices

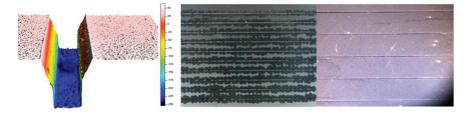

Fig 2. (a) Groove profile accomplished by UV laser; (b) EVA flowing over rear surface; (c) EVA remains within grooves

The future potential of the XIS technology makes use of thin silicon wafers that are laminated to the substrate as early as possible in the process flow to prevent handling of the extremely thin wafers as much as possible. To demonstrate the principle, however, we have used standard wafers with standard thicknesses and have performed several processing steps on wafer level before laminating the devices to

glass. Before starting the entire process flow, first several individual process steps were tested. Groove making was accomplished with a UV laser, multiple passes. In this way smooth and tapered grooves can be realized, see Fig 2 (a). To realize the first XIS demonstration devices, bonding of the strips to glass was accomplished with EVA. In first tests, EVA penetrated the grooves and was spread partly over the rear surface of the test structures, see Fig 2 (b). By adjusting lamination pressure and groove width it was realized that the EVA mainly remains in the groove, see Fig 2 (c).

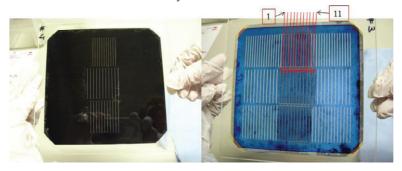

The process sequence to realize the first XIS demonstrator mini-modules was: random pyramid texture; diffusions to realize FSF and BSF; 1<sup>st</sup> SiNx ARC pass half thickness; laser grooves and laser damage removal etch; 2<sup>nd</sup> SiNx ARC pass, realizing also groove passivation; amorphous silicon intrinsic and p-type doped layer deposition; ITO sputtering; followed by lamination to glass with EVA and laser isolation and contacting and metallization. Three individual XIS mini-modules were processed from standard 156 x 156 mm<sup>2</sup> semi-square n-type Cz wafers, see Fig 3. From the front side the laser grooves can be seen, indicating the areas where the mini-modules have been realized. Three different strip widths were used, 3.0 mm (top), 4.0 mm (middle), and 3.5 mm (bottom). Only after lamination to glass the strips were cut loose from the wafer by a laser.

Fig 3. Front side (a) and rear side (b) of first realized XIS demonstrator mini-modules

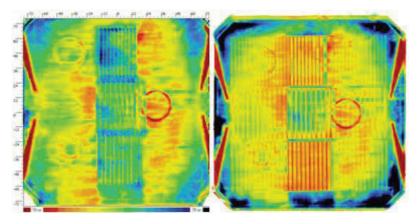

Fig 4. Lifetime of three XIS mini-modules located in the middle of the wafer, before (a) and after (b) the last rear process steps

After device preparation IV characteristics of the mini-modules were measured. The measurements demonstrate that a successful series connection of all ten cells in a mini-module has been achieved with a realized mini-module voltage of 2.6 V, measured between position 1 and 11 (see Fig 3). Maximum individual cell voltage was 0.43 V. This is the first successful demonstration of XIS devices, including the

realization of a hybrid BC-HJ structure. However, the efficiency results that were achieved are not impressive with low currents, voltages and FFs, although the best pseudo-FF that was achieved was 76%.

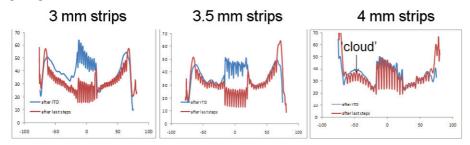

The results were analyzed further by monitoring of the minority carrier lifetimes of the devices. Two main issues were identified. One issue is that upon deposition of SiNx on the front side and in the grooves, also parasitic deposition on the rear occurs. This results in poor properties for the heterojunction emitter. Another issue that was encountered is lifetime degradation induced by the rear side laser processes. In Fig 4 the lifetimes of the mini-modules and the surrounding wafer are shown before (a) and after (b) the rear last process steps. After these steps, the lifetimes of the strips in the mini-modules was reduced. The effect of parasitic nitride deposition can best be seen in the areas of the wafer next to the mini-modules and in the 'cloud' area in Fig 5. The degradation of the lifetime as seen in Fig 4 seems the least severe for the broadest (4 mm) strips. This was investigated in some more detail. In Fig 5 a line scan of the lifetimes is shown in the direction perpendicular to the strips, before and after the rear processes. The difference in lifetime is largest for the smallest strips. We assume that this effect is due to the confinement of heat in the strips, inducing damage to the emitters after lamination of the devices to the glass plate with EVA.

Fig 5. Lifetime line scan in the direction perpendicular to the strips before (blue) and after (red) the last process steps

#### 7. Conclusions and outlook

The XIS concept has been introduced. It has the potential to achieve a significant cost reduction with high efficiency back-contact heterojunction silicon thin wafer technology, cutting down the bill of materials, almost eliminating the use of expensive metals, and thin film like, large area high throughput production technology. First laboratory devices have been made, demonstrating series connection of over ten individual hybrid back contact silicon heterojunction solar cells.

#### References

- [1] Govaerts J, Robbelein J, Gong C, Pawlak BJ, Gonzalez M, De Wolf I, et al. A novel concept for advanced modules with back-contact solar cells. *Proc.* 25<sup>th</sup> EPVSEC 2010; 3850-3.

- [2] Kinoshita T, Fujishima D, Yano A, Ogana A, Tohoda S, Matsuyama K, et al. The approaches for high efficiency hit solar cell with very thin ( $< 100 \mu m$ ) silicon wafer over 23%. *Proc.* 26<sup>th</sup> EPVSEC 2011; 871-4.

- [3] Das UK, Bowden S, Lu M, Burrows MZ, Jani O, Xu D, et al. Progress towards high efficiency all-back-contact heterojunction c-si solar cells. *Proc.* 18<sup>th</sup> Workshop on Crystalline Silicon Solar Cells and Modules 2008; 70-7.

- [4] Mingirulli N, Haschke J, Gogolin R, Ferré R, Schulze TF, Düsterhöft J, et al. Efficient interdigitated back-contacted silicon heterojunction solar cells. *Physica status solidi (RRL)* 2011;**5**;159-61.

- [5] Holmes A, Pedder J. Laser micromachining in 3D and large area applications. The Industrial Laser User 2006;45;27-9.

- [6] Zicarelli F. Fine line printing for solar cells. Proc. Technology Day Landshut 2010.