# Sensing platform based on micro-ring resonator and on-chip reference sensors in SOI

S.M.C. Abdulla\*, B.M. de Boer, J.M. Pozo, J.H. van den Berg, A. Abutan, R.A.J. Hagen, D.M.R. Lo Cascio, P. J. Harmsma

TNO, Stieltjesweg 1, 2628 CK Delft, The Netherlands

### **ABSTRACT**

This article presents work on a Silicon-On-Insulator (SOI) compact sensing platform based on Micro Ring Resonators (MRRs). In order to enable correction for variations in environmental conditions (temperature, mechanical stress etc), a study has been performed on the performance of uncoated sensing MRRs, and of SU8- and SiO<sub>2</sub>-covered reference MRRs. Excellent shielding for both cover materials has been obtained, however, water permeation into the SU8 causes a slow drift in sensor response. We believe that a user-friendly, low-cost and robust way for optical interfacing to MRR sensor chips is required for practical application in Point-Of-Care diagnostics, and that the cost and complexity of optical-electrical read-out systems must decrease. We have taken first steps to realize that vision, by building a prototype free-space optical coupling set-up, which enables non-photonic experts to characterize surface activation processes using MRRs. Moreover, we present our first steps towards on-chip read-out systems.

**Keywords:** Micro ring resonators, biosensing on chip, free space coupling, SU8, temperature compensation.

#### 1. INTRODUCTION

Highly sensitive and cost-effective biosensors which are able to do monitoring in real-time are required in many applications such as disposable Point-Of-Care, control of industrial processes and in food industry [1]. Among the various technologies available based on integrated optics such as those based on interferometry, gratings, photonic crystals, nano opto mechanical devices etc, sensors based on micro ring resonators in SOI have specific advantages such as ease in design and fabrication, ability to multiplex, cost effectiveness, smaller foot print and high sensitivity [1].

The detection principle in a MRR is based on evanescent field sensing where the interaction of a gas/ bio molecule changes the effective refractive index of the guided mode propagating in the ring waveguide, causing a shift in comb of resonance wavelengths. However, the MRRs are also sensitive to unwanted variation in environmental conditions such as temperature and mechanical stress. Hence, to enable high sensitivity, the effect on MRRs by these environmental conditions needs to be monitored and cancelled out. An effective method for this is to incorporate additional on-chip reference sensors which can monitor unwanted changes in the sensing ring's environment. This can be achieved by having two MRRs fabricated on the same chip adjacent to each other. The uncovered ring (referred to as sensing ring) measures the desired evanescent field interaction, as well as any unwanted shifts due to temperature and mechanical stress. The other ring, referred to as reference ring, is covered by a coating layer, and measures the same unwanted shifts, but not the evanescent field interaction. By comparing the two, the shift due to evanescent field interaction can be extracted. Recently [2] has reported the use of SiO<sub>2</sub> and SU8 as effective covering materials for SOI based MRRs. They have demonstrated SiO<sub>2</sub> to be excellent shielding capabilities. SU8 on the other hand requires simple processing steps, but has the drawback of slow water permeation into the layer. In this work we look further into the possibilities of using these two materials as covering layers for reference sensors towards the realization of an photonic bio/gas sensing platform with on-chip compensation for temperature and mechanical stress, and possibly with on-chip read-out optics.

\*shahina.abdulla@tno.nl; phone 318884949; fax 31-15-2612403, www.tno.nl

Silicon Photonics IX, edited by Joel Kubby, Graham T. Reed, Proc. of SPIE Vol. 8990, 89900W © 2014 SPIE · CCC code: 0277-786X/14/\$18 · doi: 10.1117/12.2039896

Proc. of SPIE Vol. 8990 89900W-1

## 1.1 Micro ring resonators

The framework of silicon photonics platform ePIXfab [3] has been utilized for fabricating micro-ring resonators, integrated with Out-Of-Plane grating couplers for optical interfacing. The devices are fabricated on a SOI wafer, using 193 nm deep-UV lithography process. The substrate was thinned to 250  $\mu$ m after processing. The silicon device layer in the ePIXfab framework has a thickness of 220 nm, situated on a 2.0  $\mu$ m thick SiO<sub>2</sub> bottom cladding. The waveguide width is 450 nm wide, so that the MRRs are single mode for TE polarized light at a wavelength of 1550 nm. No top cladding was applied to the devices, other than photo resist for temporary protection during dicing, and native oxide that will appear on an Si surface naturally. We used Multimode Interference (MMI) couplers to couple light between the ring and a straight bus waveguide, which is a very robust design approach. The MMI length and width are 57.15  $\mu$ m and 6.9  $\mu$ m, respectively.

Figure 1: Microscopic image of the MRRs fabricated in SOI

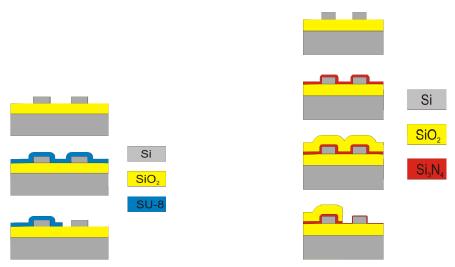

Following the MRR fabrication, the wafer is diced into smaller pieces of  $1.0 \times 1.4$  cm each for post processing. Optimized post-processing steps to deposit 2  $\mu$ m thick SU8 and SiO<sub>2</sub> layers on reference rings has been developed (Table 1Table 2). The process step for SU8 coating is straight forward, requiring only to spin coat SU8 and then to selectively remove it. The measured thickness of the SU8 layer deposited for this experiment is  $1.95\mu$ m. SiO<sub>2</sub> on the other hand requires a thin Si<sub>3</sub>N<sub>4</sub> layer to be pre-deposited as an etch stop layer for its plasma etching step. Without this etch stop, the SiO<sub>2</sub> buffer layer underneath the waveguides may be etched while locally removing the shielding SiO<sub>2</sub> layer, causing serious modification of the mode properties. However, this also results in a thin Si<sub>3</sub>N<sub>4</sub> layer remaining on the sensing ring, which will slightly reduce the sensitivity of the sensing ring. The measured thickness of the Si<sub>3</sub>N<sub>4</sub> layer and the SiO<sub>2</sub> layers are 184 nm and 1787 nm, respectively, resulting in total covering layer thickness of 1971 nm. Figure 1 shows a microscopic image of the fabricated MRRs together with their access waveguides. The chip contains many different types of rings, we see circular (top row), folded straight (center row) and square rings (lower row), designed to support a variety of applications. In our experiment, the upper row was used for the uncovered sensing rings, and the second row was used for the covered reference rings. Figure 2 shows a schematic of the post-processing steps performed on the SOI MRRs to realize the covered reference rings.

Table 1. The process flow for depositing SU8

| Table 1. The process flow for depositing 508 |                          |                                                                                     |

|----------------------------------------------|--------------------------|-------------------------------------------------------------------------------------|

| Steps                                        | Process                  | Parameters                                                                          |

|                                              |                          |                                                                                     |

| 1                                            | Dicing                   | Die size 1.0 x1.4 cm                                                                |

| 2                                            | Remove resist protection | Rinsing with Acetone and Iso propyl Alcohol (IPA).                                  |

|                                              | layer                    |                                                                                     |

| 3                                            | Dehydration              | In hotplate at 200 °C for 10 min                                                    |

| 4                                            | SU-8 coating             | Spin resist SU-8 at 2000 rpm (to get a layer thickness of 1.95 μm); Soft bake for 1 |

|                                              |                          | min at 65 °C.                                                                       |

| 5                                            | Exposure                 | Exposure time 13 sec; Post Exposure Bake 1 min at 65 °C for 1 minutes.              |

| 6                                            | Developing and           | Time:1 min in SU-8 developer and rinse with IPA and dry.                            |

|                                              | inspection               |                                                                                     |

Proc. of SPIE Vol. 8990 89900W-2

Figure 2. A schematic illustration of the post processing steps performed on the SOI devices to deposit the covering layers. The left picture shows the steps for a SU8 coating whereas the right picture shows that for a  $SiO_2$  coating.

Table 2. The process flow for depositing SiO<sub>2</sub> layer

| Step | Process                                    | Parameters                                                                                                                                                                                                                                                             |

|------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Dicing                                     | Die size 1.0x1.4 cm                                                                                                                                                                                                                                                    |

| 2    | Remove protection layer and cleaning       | Rinsing with Acetone and IPA.                                                                                                                                                                                                                                          |

| 3    | PECVD Si <sub>3</sub> N <sub>4</sub> layer | Temperature: 300°C; N <sub>2</sub> flow 300 sccm, Pressure 1000 mtorr; SiH <sub>4</sub> flow:20 sccm; NH <sub>3</sub> flow:20 sccm; N <sub>2</sub> flow:980 sccm; Pressure:650 mtorr; Grow rate Si <sub>3</sub> N <sub>4</sub> 13 nm/min                               |

| 4    | Thickness measurement                      | Woollam ellipsometer                                                                                                                                                                                                                                                   |

| 5    | PECVD SiO <sub>2</sub> layer               | Temperature: 300°C; N <sub>2</sub> flow 300 sccm, Pressure 1000 mtorr; SiH <sub>4</sub> flow:8.5 sccm; N <sub>2</sub> O flow:710 sccm; N <sub>2</sub> flow:162.5 sccm; Pressure:1000 mtorr; RF power:20 W; Reflected power:1 W; Grow rate SiO <sub>2</sub> 72.5 nm/min |

| 6    | Thickness measurement                      | Woollam ellipsometer                                                                                                                                                                                                                                                   |

| 7    | Photoresist (AZ5214)coating                | Spin HMDS; 3000 rpm; 2 min hotplate 175°C; Spin resist AZ5214; 1300 rpm (layer thickness 2.2 µm); soft bake for 30 min at 90 °C                                                                                                                                        |

| 8    | Exposure                                   | Exposure Time: 9 sec; Soft contact.150 mJ/cm <sup>2</sup>                                                                                                                                                                                                              |

| 9    | Developing                                 | Time:120 sec and hard bake for 30 min at 125°C                                                                                                                                                                                                                         |

| 10   | Etching SiO <sub>2</sub> layer             | Pressure 2.6x $10^{-3}$ mbar; RF1 2500 W; SH RF2 300 W; Bias 37.5V; Gas flow $C_4F_8$ : 20 sccm; $H_2$ 100 sccm; $C_4F_4$ 10 sccm; Etch rate $SiO_2$ : 216 nm/min and Etch rate $AZ5214$ :131 nm/min.                                                                  |

| 11   | Remove resist remaining's                  | Rinsing with Acetone and IPA.and drying                                                                                                                                                                                                                                |

# 2. CHARACTERISATION

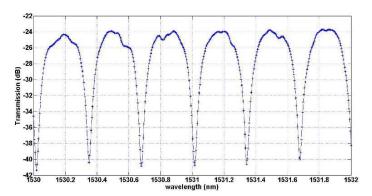

Transmission spectra of the MRR were measured using a C-band (near 1550 nm) broad-band source (Er-doped ASE source) in combination with an optical spectrum analyzer. The photonic chip is mounted on a Peltier element for accurate temperature control. Figure 3 shows a typical spectrum of one of the MRR before post-processing. The Free Spectral Range (FSR) is 500 pm, and the on-off ratio is better than 15 dB.

Figure 3. A measured through port transmission spectrum of a MRR before post-processing.

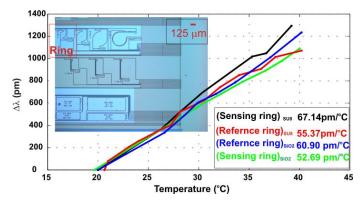

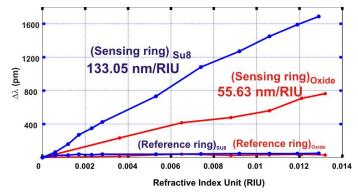

The transmission spectra of both the sensing ring and the reference rings are measured at different temperatures. The temperature is varied from 20 °C to 40 °C in steps of 2 °C and the change in its resonance wavelength is monitored. Figure 4 shows the change in resonance wavelength with respect to temperature for both the sensing and the reference rings, both for SU8 and SiO<sub>2</sub> covering layers. The sensing rings show a sensitivity of 67.1 pm/°C and 52.7 pm/°C for the SU8 processed chip and the SiO<sub>2</sub> processed chip, respectively. The difference of nearly 15 pm/°C is quite remarkable. Possibly, this is caused by the remaining thin Si<sub>3</sub>N<sub>4</sub> layer on the SiO<sub>2</sub> processed chip. It indicates that for high accuracy sensing the temperature sensitivity should be calibrated, not on every sample, but possibly from batch to batch. Also the temperature sensitivity of the reference rings varies a bit, from 55.4 pm/°C and 60.9 pm/°C for the SU8 processed chip and the SiO<sub>2</sub> processed chip, respectively, again indicating the need for prior calibration. Also the dependence will depend on the ambient (aqueous or air-like). Still, the effect of temperature on all four rings are comparable, indicating that both coatings are good candidates as reference rings. Further, the effect of ambient index change on the MRRs has been measured for both SU8 and SiO2 processed chips as given in Figure 5, by measuring the response to varying salt concentrations in de-ionized water. For both cases; as required, the reference rings are unaffected by the ambient index change. However in the case of the sensing rings, there is a substantial reduction in ambient index sensitivity for a SiO<sub>2</sub> processed chip compared to that of an SU8 processed chip. This is attributed by the presence of the Si<sub>3</sub>N<sub>4</sub> etch mask layer still remaining on the sensing ring.

Figure 4. Effect of temperature on change in resonance wavelength of sensing and reference MRRs with the microscopic image of MRRs shown in inset.

Figure 5. Effect of ambient index on change in resonance wavelength of sensing and reference MRRs.

We also analyzed the stability over time of the SU8 and  $SiO_2$  cover layers in water, and found that the SU8 causes a slow drift in MMR response over tens of pm due to water permeation, until stabilization occurs after approximately 40 minutes. In practice, this would mean that a measurement is done during this drift, and should not take longer than 1-2 minutes, or each sensor would need a 'wetting' time of 1 hour at least. In practice, both strategies are rather inconvenient, and we believe that  $SiO_2$  cover layers are preferred.

## 3. OUTLOOK: OPTICAL COUPLING AND ON-CHIP INTERROGATION

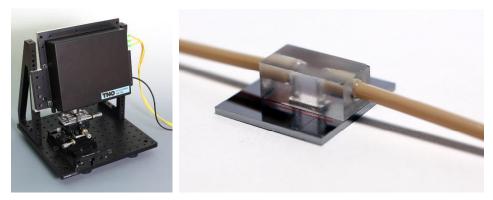

We have developed a concept to have a low-cost, robust and user-friendly multi-channel optical connection to a chip (Figure 6). Non-photonic experts can perform photonic chip characterization within only a few hours of training. The system is free from close-proximity fibers to establish the optical connection, since these typically get damaged rather easily. Placing a chip with a flow cell in the device, getting it aligned, and starting the measurement is a matter of typically 2 to 3 minutes. The system can be upgraded with thermal control, more optical channels, and is suitable for miniaturization: the current system is the size of a desk top PC, however, we envision implementation the size of a mobile phone.

Figure 6. Picture of FRESCO set-up and chip with flow cell

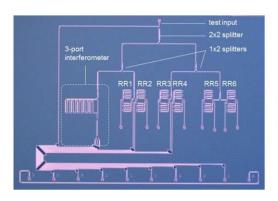

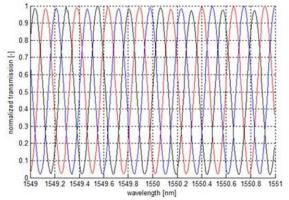

The main cost driver for a read-out system is in the optics. Either one needs a broadband light source in combination with a spectrometer, or a scanning narrow-band source in combination with a broadband detector. Typically, the spectrum analyzer cannot meet a 1 pm resolution or better, and tunable lasers costs several 10s of k\$. We believe that the most cost-effective way to have a small-size read-out unit is to make use of a low-cost tunable laser. This can be a temperature-tuned DFB laser for example (speeds in the order of 1 Hz are typically OK), or a Vertical Cavity Surface Emitting Laser (VCSEL), the wavelength of which depends strongly on the drive current. A tuning range of a few times the MRR FSR, so typically a few nm at most, is sufficient. To achieve high accuracy, real-time wavelength tracking of the scanning laser wavelength is essential. We have a large experience in the use of 3-port interferometers for wavelength tracking, both in fiber-optics and in integrated optics. We have taken first steps to incorporate on-chip reference sensors and a 3x3 interferometer [4,5] in obtain a single integrated sensing platform. The 3-port interferometer enables on chip interrogation for this sensing platform, with its three outputs which are at a 120° mutual phase difference.

This makes sure that at any input wavelength there is at least one output which has sufficient amplitude and a derivative with respect to wavelength. In our current tests, the interferometer provides a wavelength accuracy in the order of 1% of its periodicity, which can be easily tuned by customizing the optical path length difference. This sensing platform with its on-chip reference sensor, on-chip interrogator and optical coupling platform will give rise to a new step towards the commercialization of cost effective, multiplexed cheaper solutions for gas and bio sensing.

Figure 7: A microscope image of a sensing platform which consists of six MRRs and a 3x3 interferometer (left), and interferometer response (right).

## 4. CONCLUSIONS

We report on the development of a Silicon-On-Insulator (SOI) compact photonic sensing platform. The sensor elements are Micro Ring Resonators (MRRs), integrated with reference MRRs on a single chip. We have developed a dedicated easy-to-use optical coupling setup to enable testing without the need for tedious fiber-chip attachment. In order to enable correction for variations in environmental conditions such as temperature and mechanical stress, we have studied the performance of uncoated sensing MRRs, and of SU8- and SiO2-covered reference MRRs. The sensitivity to ambient refractive index was determined by measuring the response to varying salt concentrations in de-ionized water, and ranges from 50 to 130 nm/RIU depending on the MRR configuration. The reference MRRs showed negligible sensitivity to ambient index. We also analyzed the stability over time of the SU8 and SiO2 cover layers in water, and found that the SU8 causes a slow drift in MMR response over tens of pm due to water permeation, until stabilization occurs after approximately 40 minutes. Even though the use of SU8 is beneficial for ease of processing and costs, we believe that SiO2 is the material of choice for typical applications. In addition, we present our optical coupling set-up, which enables us to quickly align and perform tests on MRR sensors, typically in combination with microfluidic flow cells. The platform allows non-photonic experts to characterize surface activation processes using MRRs. We believe that such a concept is essential for the use of MRRs in biosensing research.

## **REFERENCES**

- 1. Carmen Estevez, M., Alvarez, M. and Lechuga, M., "Integrated optical devices for lab-on-a-chip biosensing applications," Laser Photonics Rv. 6(4), 463-487 (2012).

- 2. Xu, D.X., Vachon, M., Densmore, A.,Ma, R.,Janz, S.,Delâge, A.,Lapointe, J.,Cheben, P.,Schmid, J.H.,Post, E., Messaoudène, S., and Fédéli, J.M., "Real-time cancellation of temperature induced resonance shifts in SOI wire waveguide ring resonator label-free biosensor arrays," Optics Express 18(22), 22867-22879 (2010).

- 3. Dumon, P., Bogaerts, W., Baets, R., Fedeli, J.M., and Fulbert, L., "Towards foundry approach for silicon photonics: silicon photonics platform ePIXfab," Electron. Lett, Vol 45(12), 581-582 (2009).

- 4. Harmsma, P.J., Staats, J., Lo Cascio, D., Cheng, L., "Three-port interferometer in silicon-on-insulator for wavelength monitoring and displacement measurement", Proc. CLEO Europe, Munich, CK.P.26 TUE (2011).

- 5. Abdulla, S.M.C., De Boer, B, Pozo, J.M, S.M.C., Lo Cascio, D., Harmsma, P., "SOI and InP based on-chip 3x3 interferometers for wavelength interrogation" Proc. IEEE Photonics Benelux Society, 25-26 November (2003).

Proc. of SPIE Vol. 8990 89900W-6